STA笔记

静态时序分析只能用于同步电路,主要验证寄存器的建立时间和保持时间是否满足要求

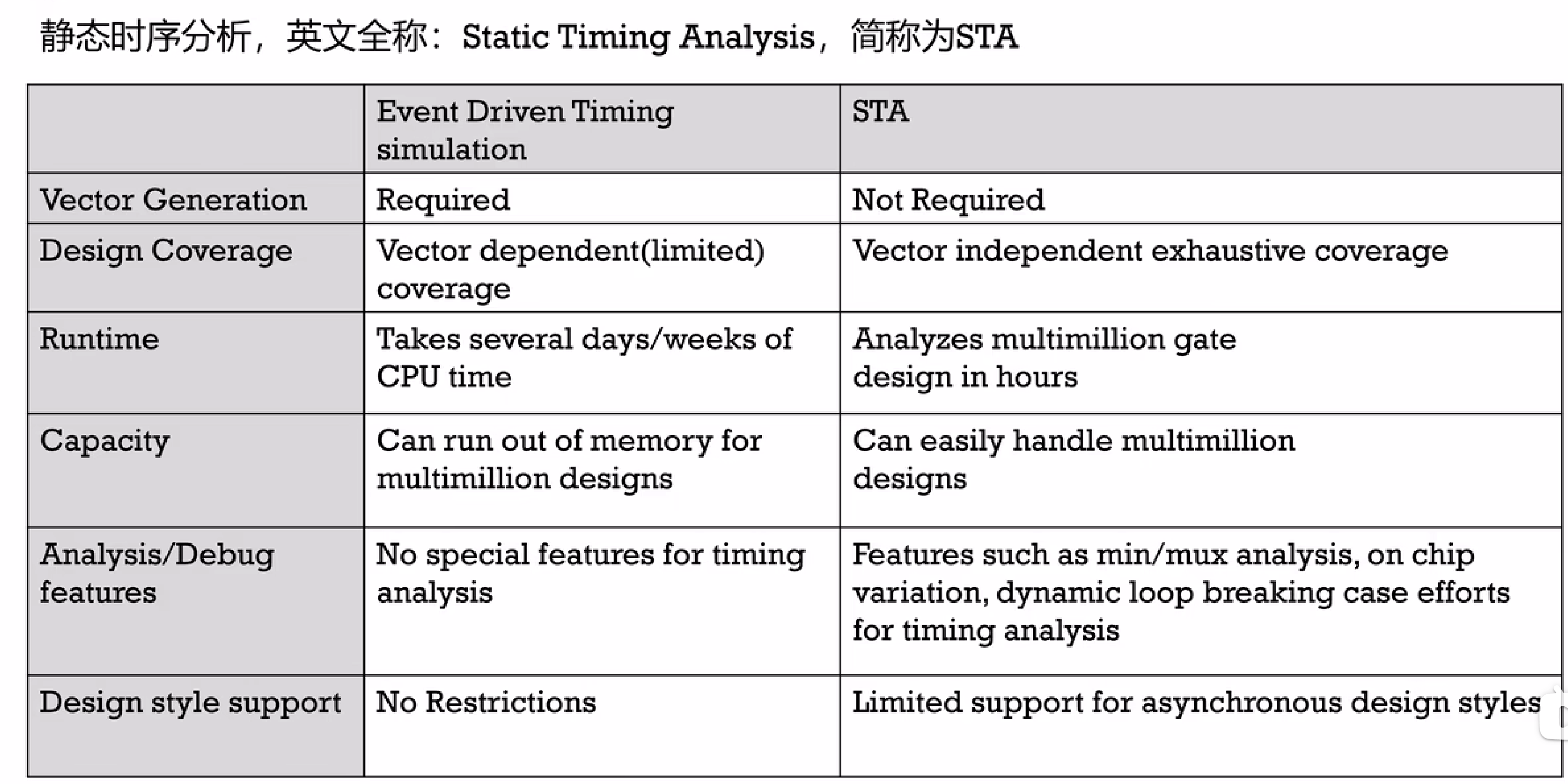

静态时序分析与功能仿真的区别

TCL

变量

$符号表示变量置换,tcl会认为$后面的符号是变量名,将变量置换成它的值

[]内是一个独立的tcl语句,如

1 | set a [expr 3+4] |

tcl解释器会对双引号中的$和[]符号进行变量替换和命令置换,而在花括号中,所有字符都是普通字符

1 | puts "\t[expr $x + $y]" |

特殊符号加上反斜杠\后会被置换成普通字符

定义变量set与取变量值$

1 | set cell "bufx2" |

1 | set cell "bufx2" |

数组与列表

定义数组,array关键字可以用来获取数组信息

1 | set cell(ref1) "bufx2" |

定义列表与常用列表方法

1 | set cell1 {a b c} |

列表排序

1 | set list1 {4 5 3} |

tcl支持的数学运算,expr命令用于求值

1 | + - * / >= <= != == |

控制流

控制流语句:if elseif else

1 | if{$l == 3} { |

foreach,可以用break结束循环,continue继续循环

1 | foreach i $list { |

while循环,incr关键字用于递增或递减变量

1 | while {$i < 3} { |

for循环,和c语言类似,需要初始参数,循环条件与重新初始化参数

1 | for {set i 3} {$i > 0} {incr i -1} { |

函数

使用proc来定义函数,可以有参数和返回值

1 | proc add {a, b} { |

在函数中引用外部变量需要加global关键字

1 | set cin 1 |

正则表达式

使用关键字regexp来进行设置查询,下面是常用用法,将正则表达式匹配的值放在第一个参数,正则表达式括号中的匹配值保存在后续参数

1 | set str "ade 12 er" |

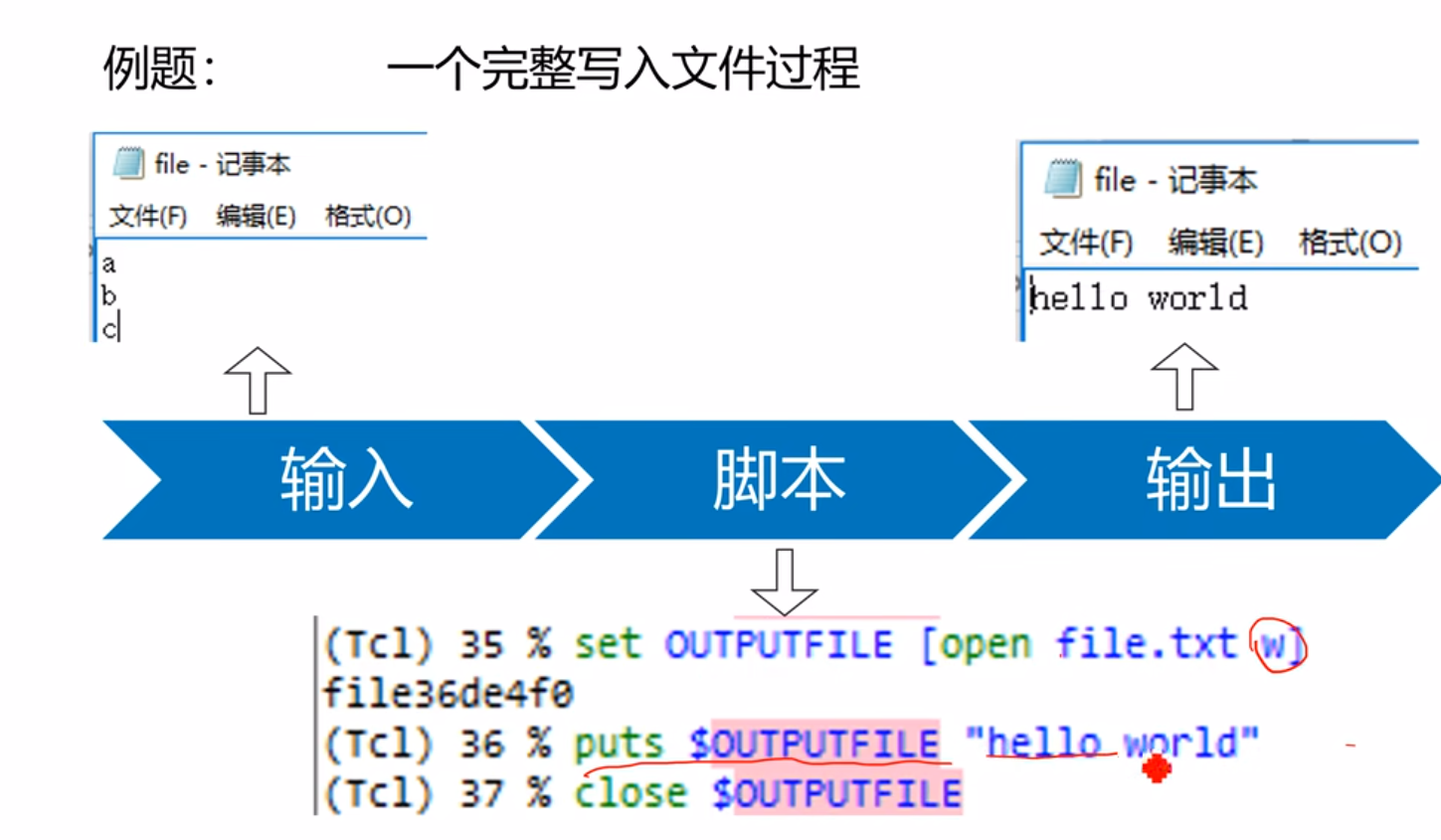

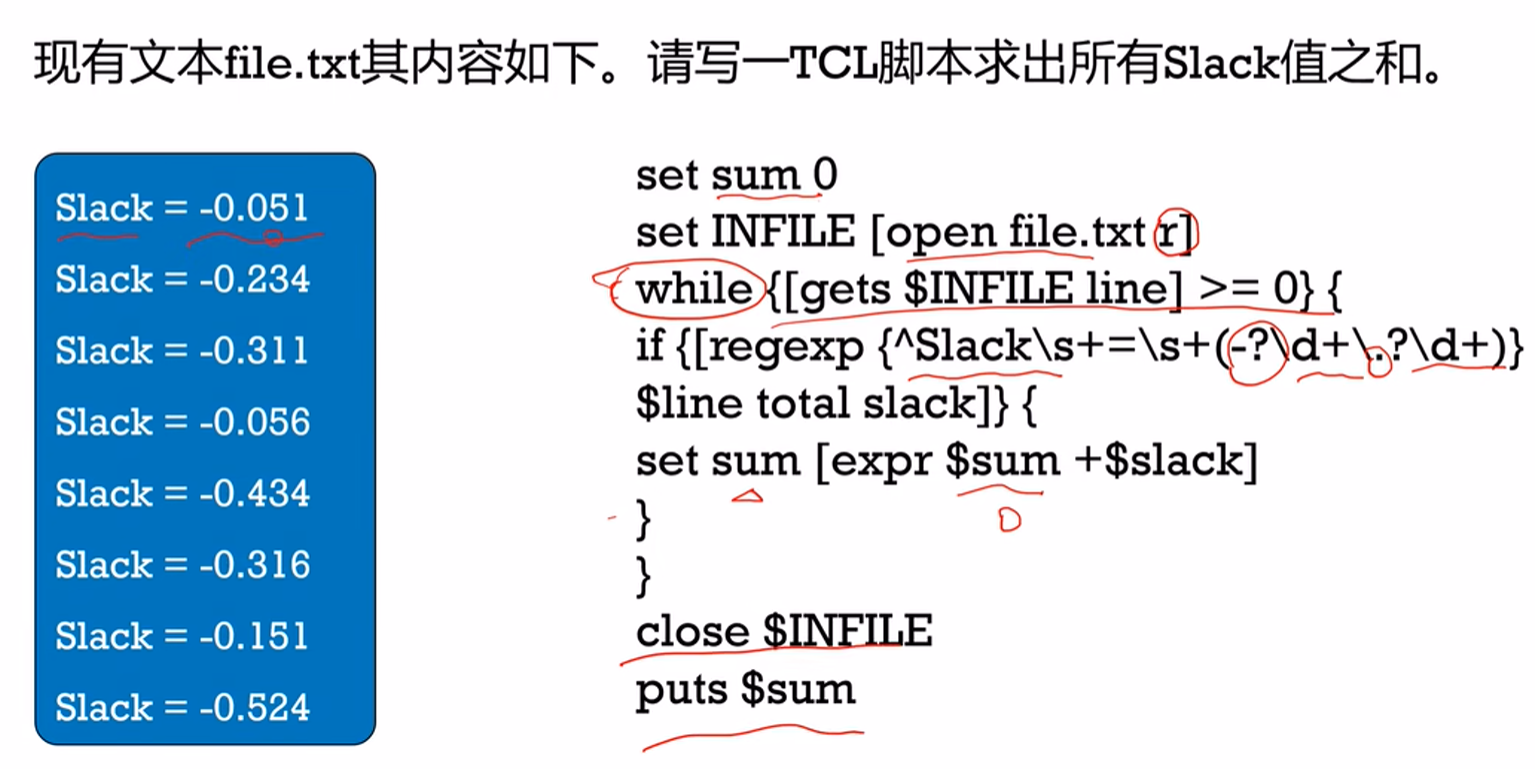

文本处理

使用open打开文件,puts写入文件,gets读取文件,close关闭文件

一个例题

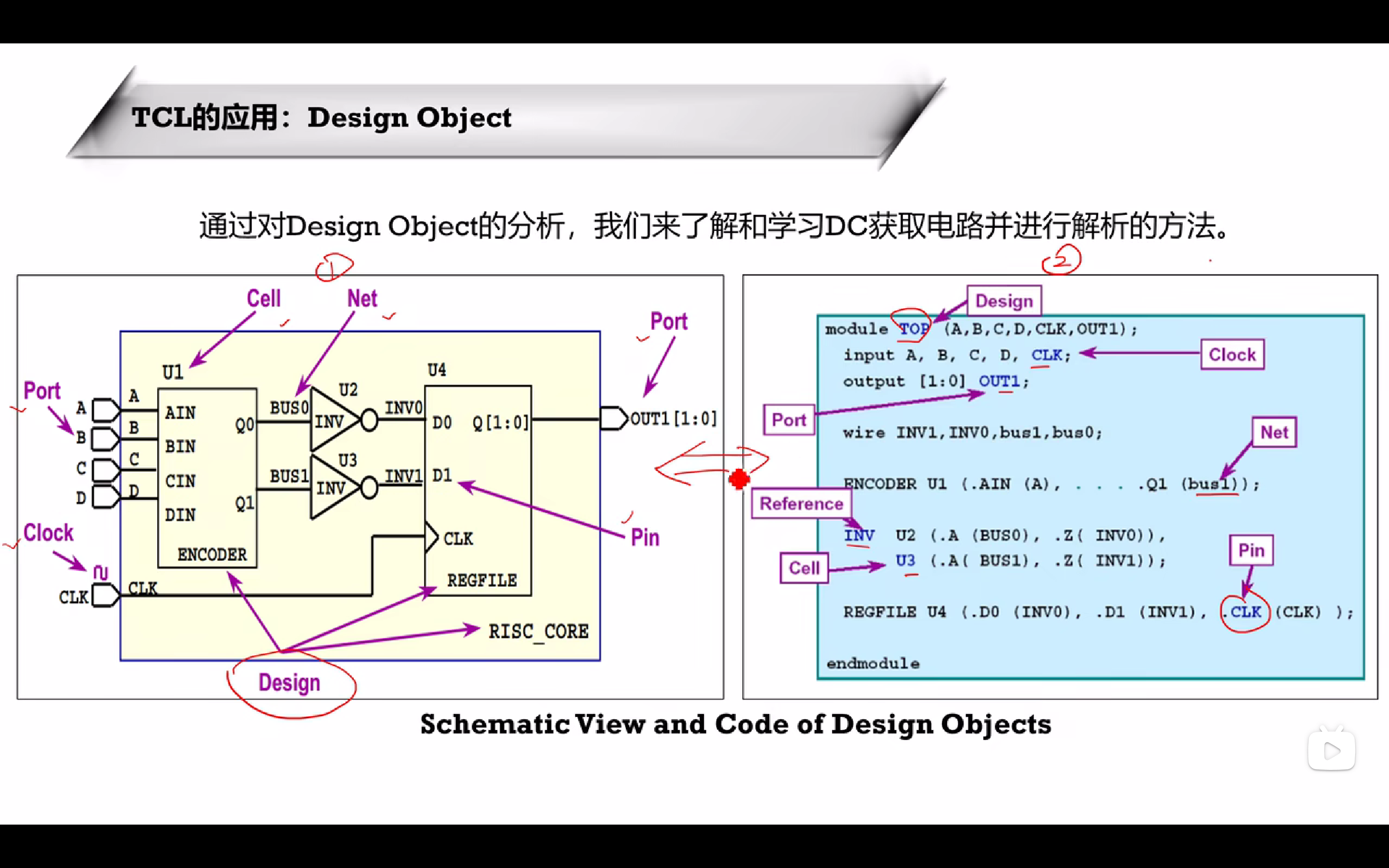

Synopsys TCL

一个设计里面都是design object,包括net、cell等等object

可以用get_cells,get_ports,get_nets,get_pins等等指令得到对应的object集合

1 | get_ports * |

求数量指令sizeof_collection,等价于先使用get_object_name转换为列表再求长度

1 | sizeof_collection [gets_nets *] |

每个object都有自己的属性,使用get_attribute来获取对象的属性

1 | get_attribute [get_cells -h U3] ref_name # cell有ref的名字 |

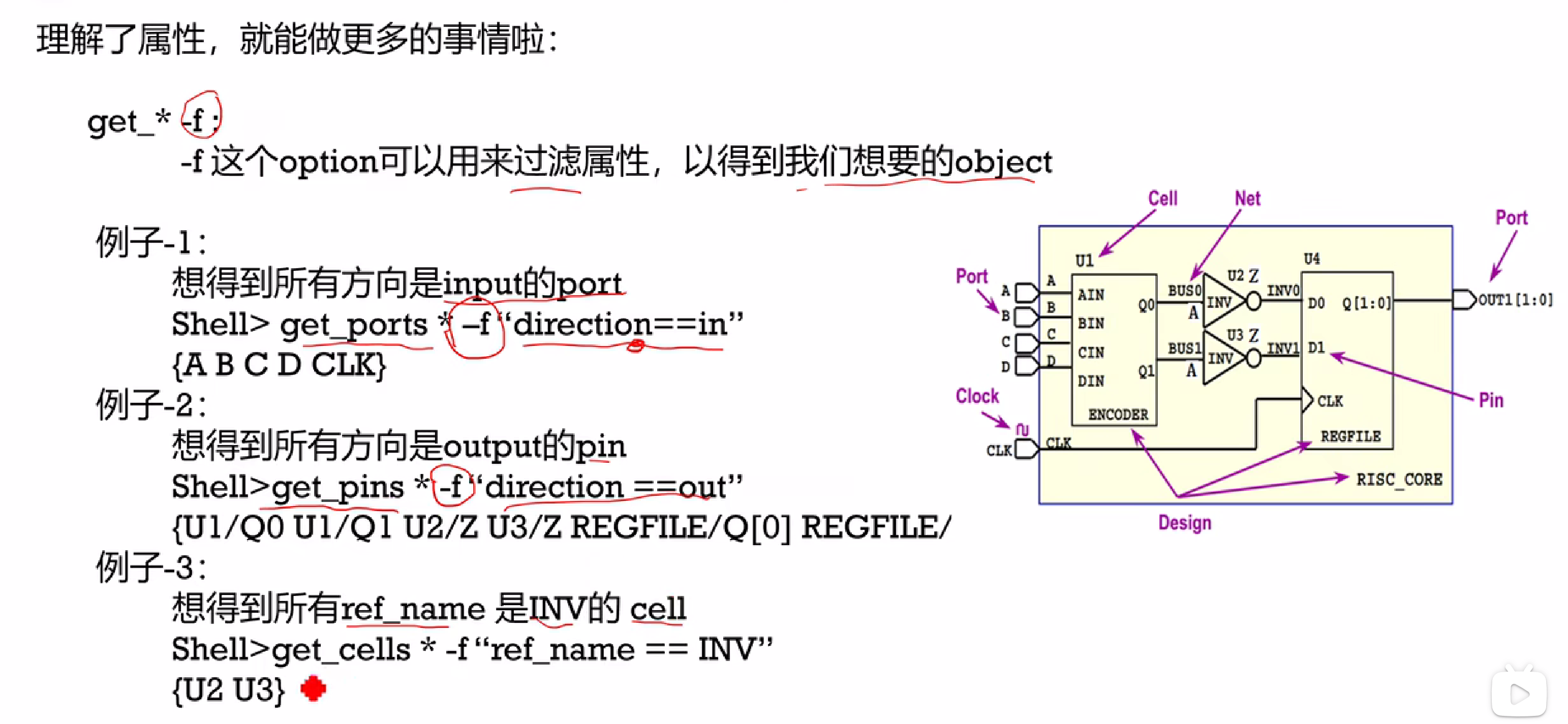

根据属性匹配

查找与对应object相连的object

STA

PrimeTime(pt)用于STA

静态时序分析就是将电路划分成各个时序路径,分析每条路径的建立时间和保持时间是否满足要求。

时序弧

静态时序分析是基于timing arc数据的时序分析。时序弧是用来描述两个节点延时信息的数据,时序弧的信息分为连线延时和单元延时。

- 连线延时是单元输出端口和扇出网络负载之间的延时信息;

- 单元延时是单元输入端口到输出端口的延时信息。因此一条完整路径的时序信息计算由连线延时和单元延时组成。

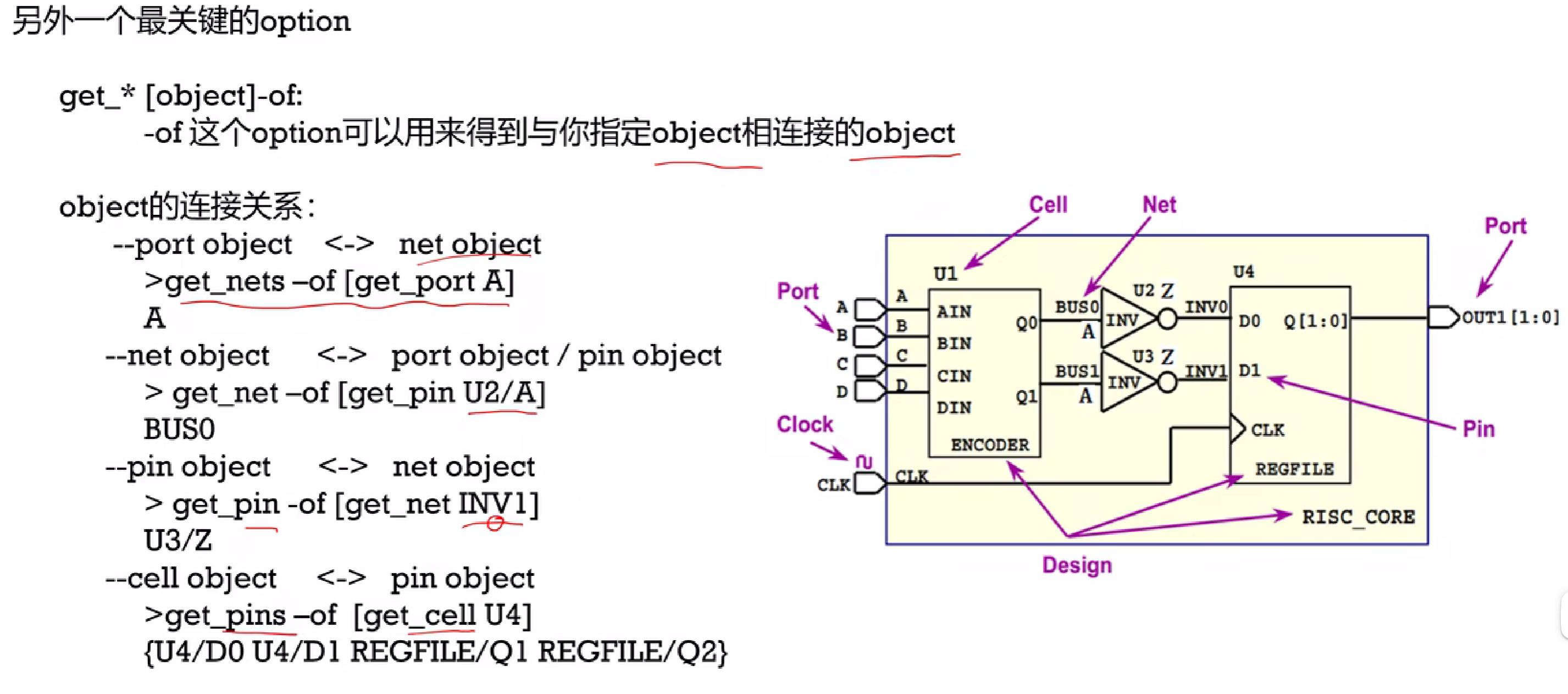

时序路径

时序路径

- 起点:触发器时钟引脚、输入端口

- 终点:触发器数据输入引脚、输出端口

时序路径类型共有4种:

- clk->D

- clk->output_port

- input_port->D

- input_port->output_port

一个时钟域内是同步的,时钟域之间是异步的,全局异步,局部同步。跨时钟域的电路需要进行约束,不进行静态时序分析。

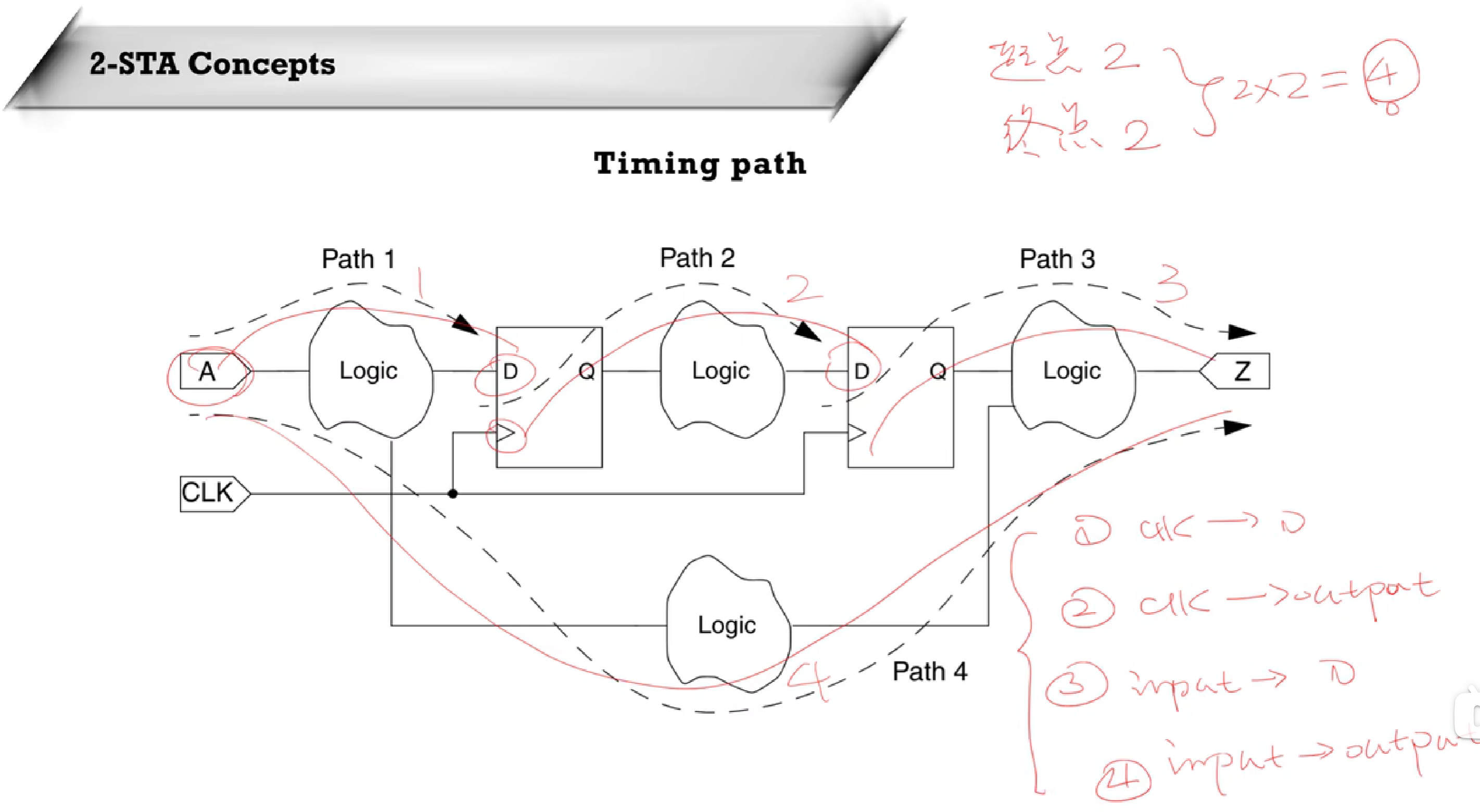

PVT环境

需要指定PVT环境才能进行STA,PVT是指工艺制程(process)、电压(voltage)和温度(temperature)。

提供三种PVT环境:WCS(Worst-Case Slow)、TYP(Typical)和BCF(Best-Case Fast)。WCS和BCF环境是工厂制造制程的两种极端情况。

下图是PVT与延迟的关系:

在最慢的条件下检查setup,在最快的条件下检查hold

- 在电压最小,温度最高的条件下(ss),延迟最大,检查setup

- 在电压最高,温度最低的条件下(ff),延迟最小,检查hold

使用tcl指定pvt环境

1 | set_operating_conditions "WCCOM" -library mychip |

标准单元库

单元库文件的格式:lib、db

时序模型

时序模型分为线性时序模型和非线性时序模型。

延迟与输入转换时间(input transition)和输出负载(output load)有关

线性时序模型如反相器。通过输入转换时间和输出负载的值就可以计算出器件对应的单元延迟。通常情况下,延迟随着这两个参数提升。线性时序模型:$D = D_0 + D_1 \times S + D_2 \times C$

非线性时序模型(NLDM,None-Linear Delay Model)通过查找表来计算单元延迟。NLDM模型都是通过input transition和output load可以在查找表中找到cell delay以及output transition。

组合单元模型

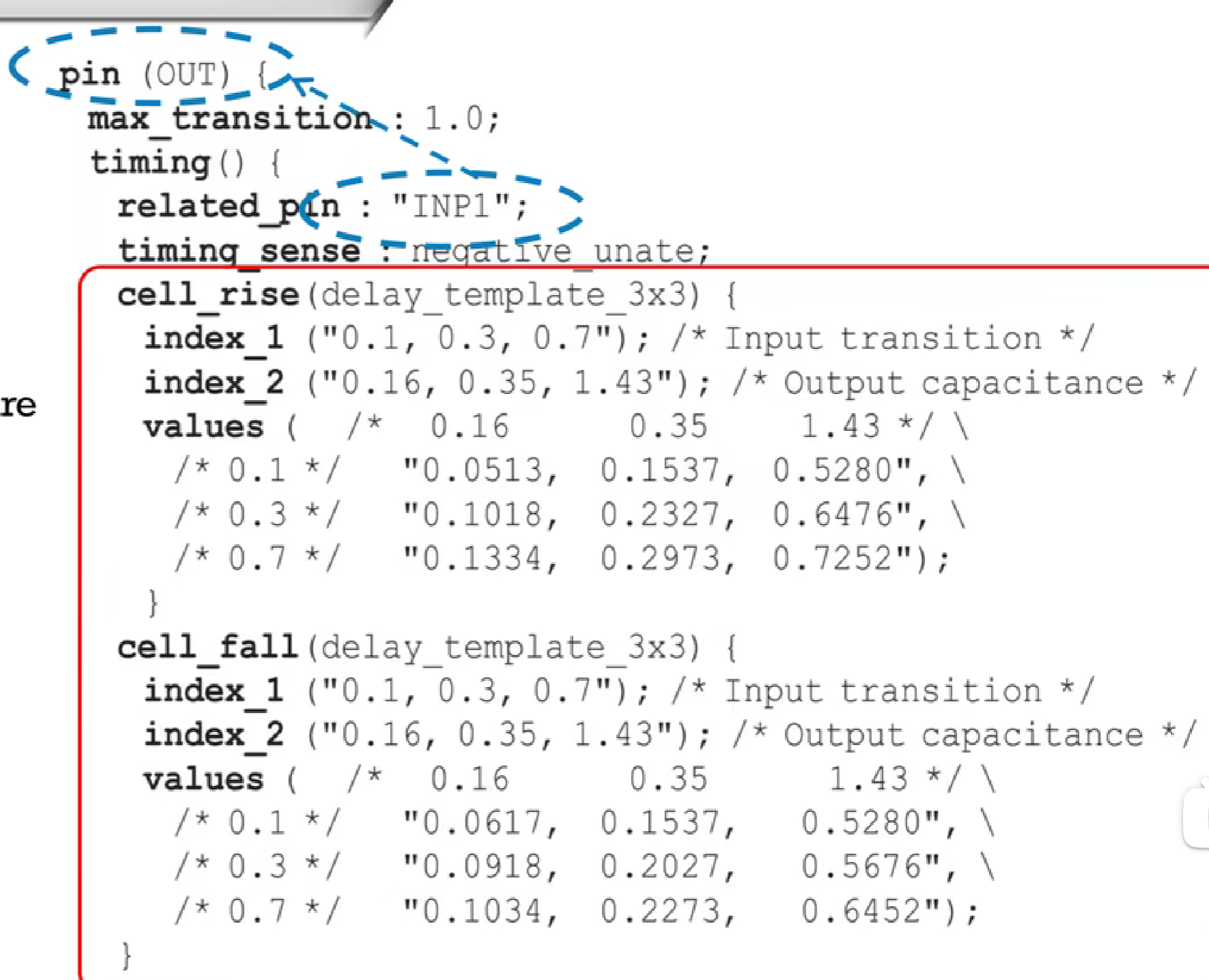

下面是NLDM的一个组合逻辑单元的例子。图中显示了从INP1引脚到OUT引脚的延迟查找表。

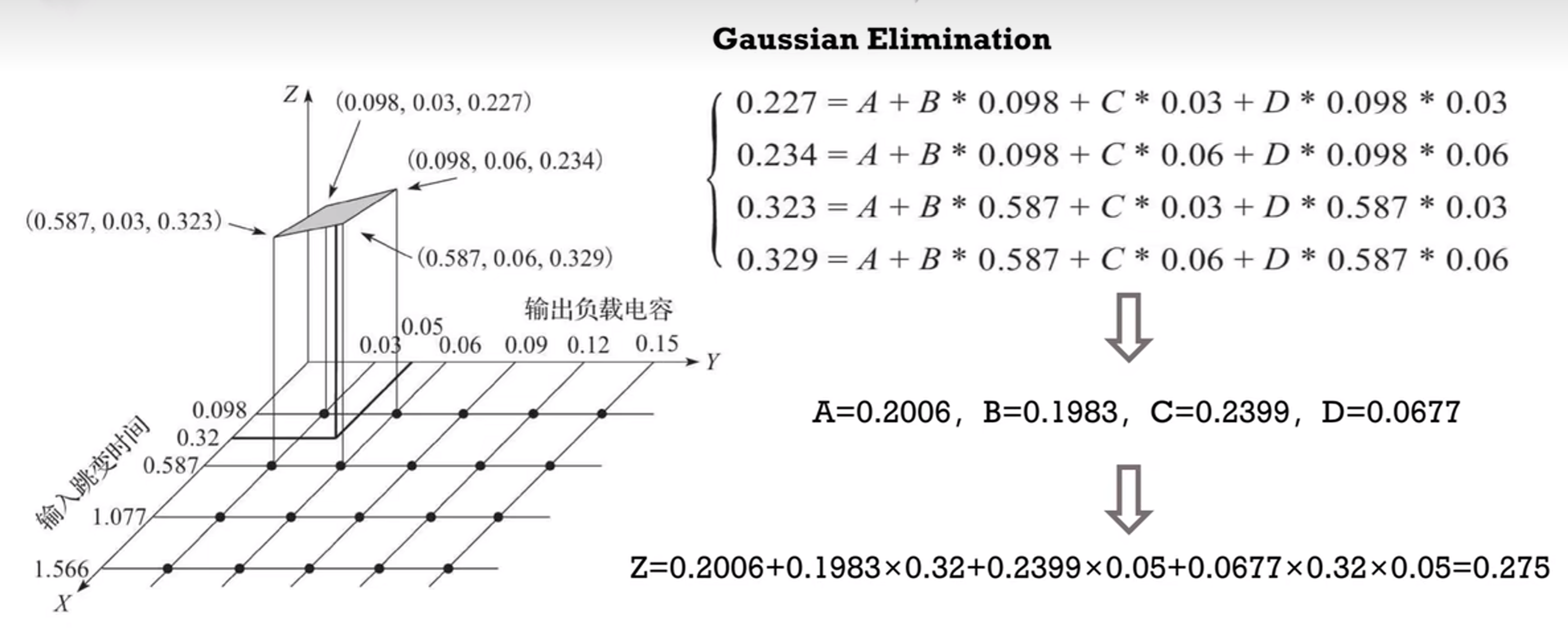

如果索引没有在查找表内,则需要使用高斯消元法来进行计算,如下面的例子,输入跳变的值和输出负载的值分别为0.32与0.05,没有在查找表内。

库里定义了一个参数slew_derate。该参数说明,库中算出来的转换时间需要再乘以个0.5才是实际的转换时间。现在的转换时间与建库时定义的转换时间发生了变化。

1 | slew_derate_from_library : 0.5; |

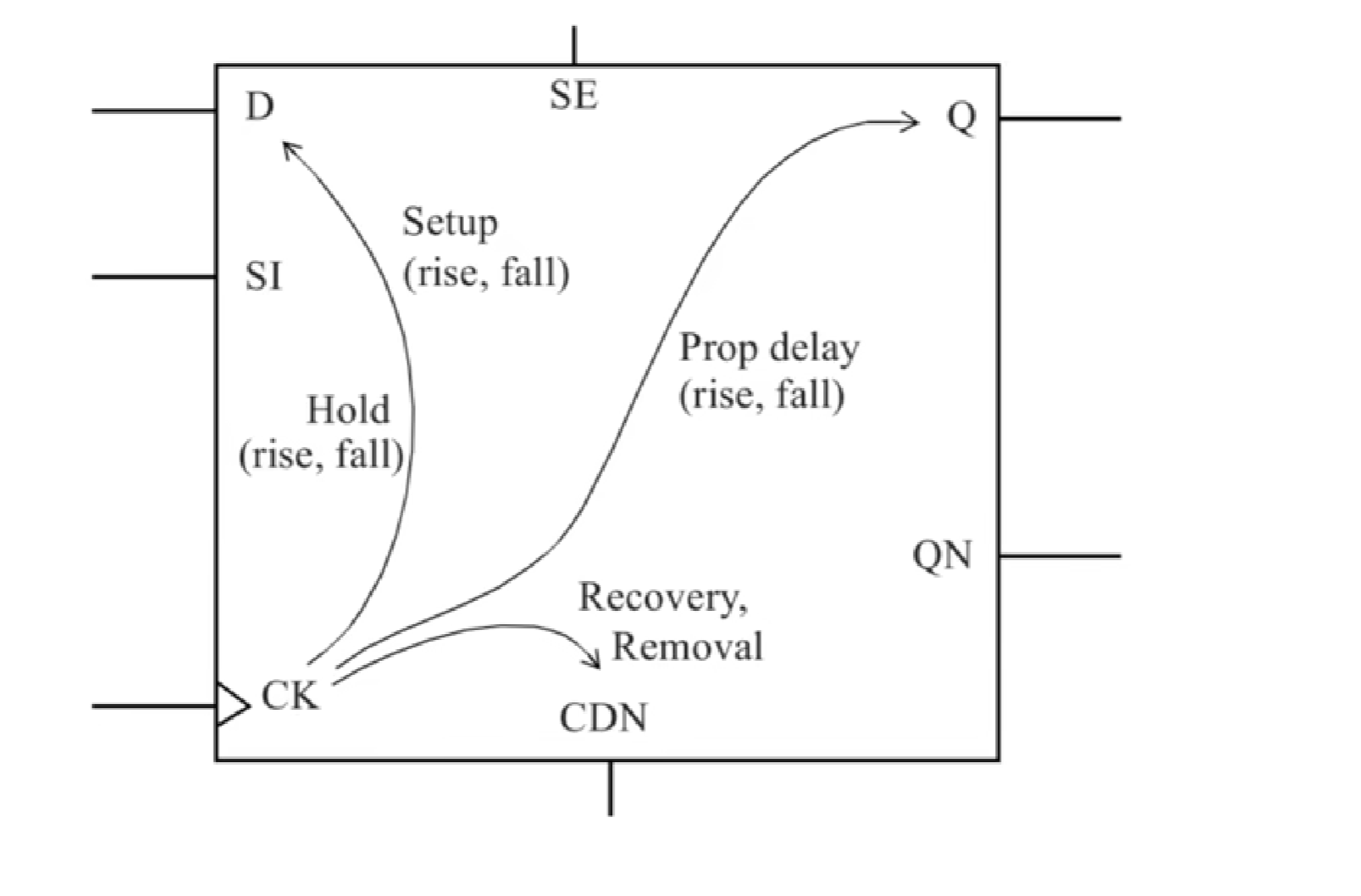

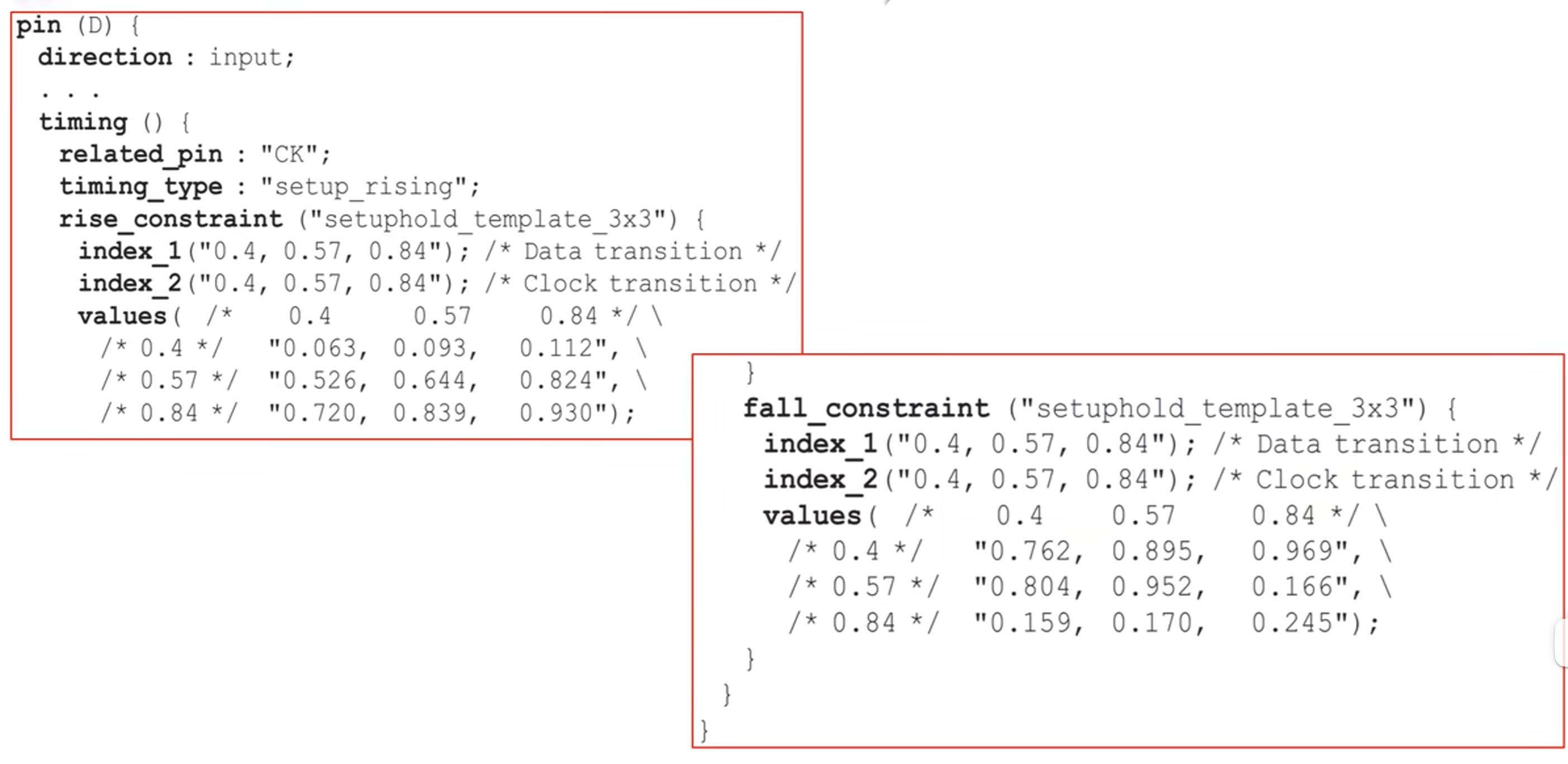

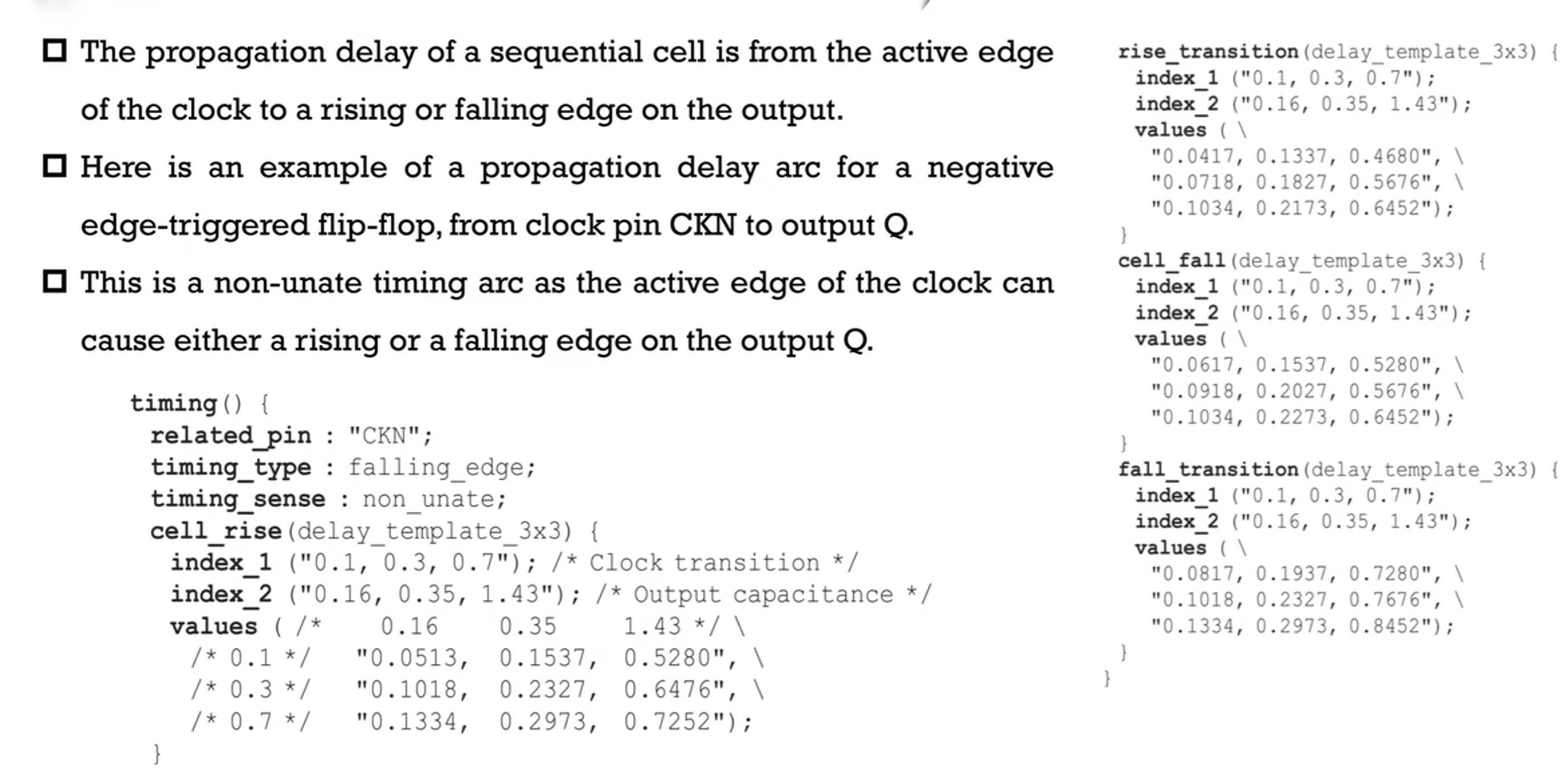

时序单元模型

时序单元有clk引脚到D引脚的setup与hold的约束信息,以及异步端口上的recovery与removal的约束信息。

有clk到Q引脚的延迟信息。

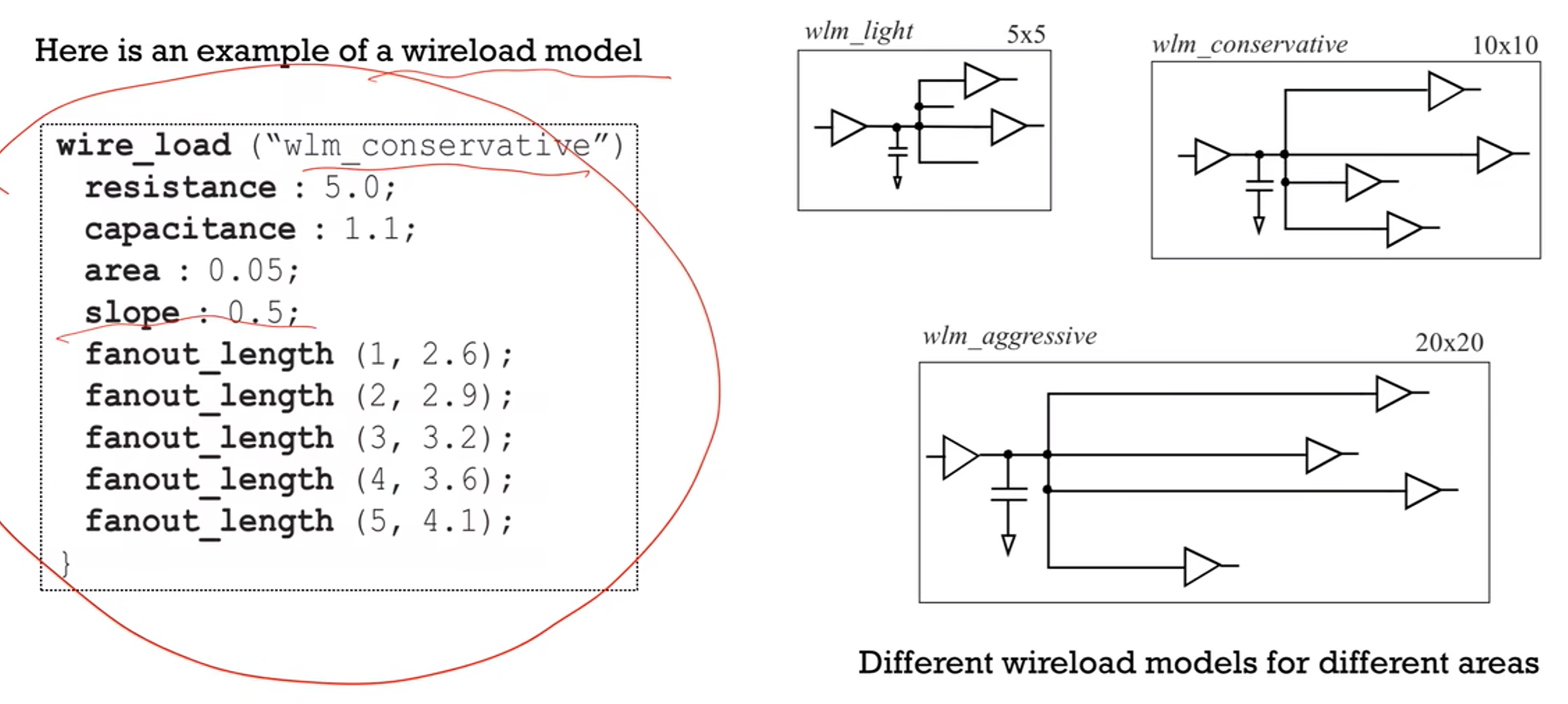

线载模型

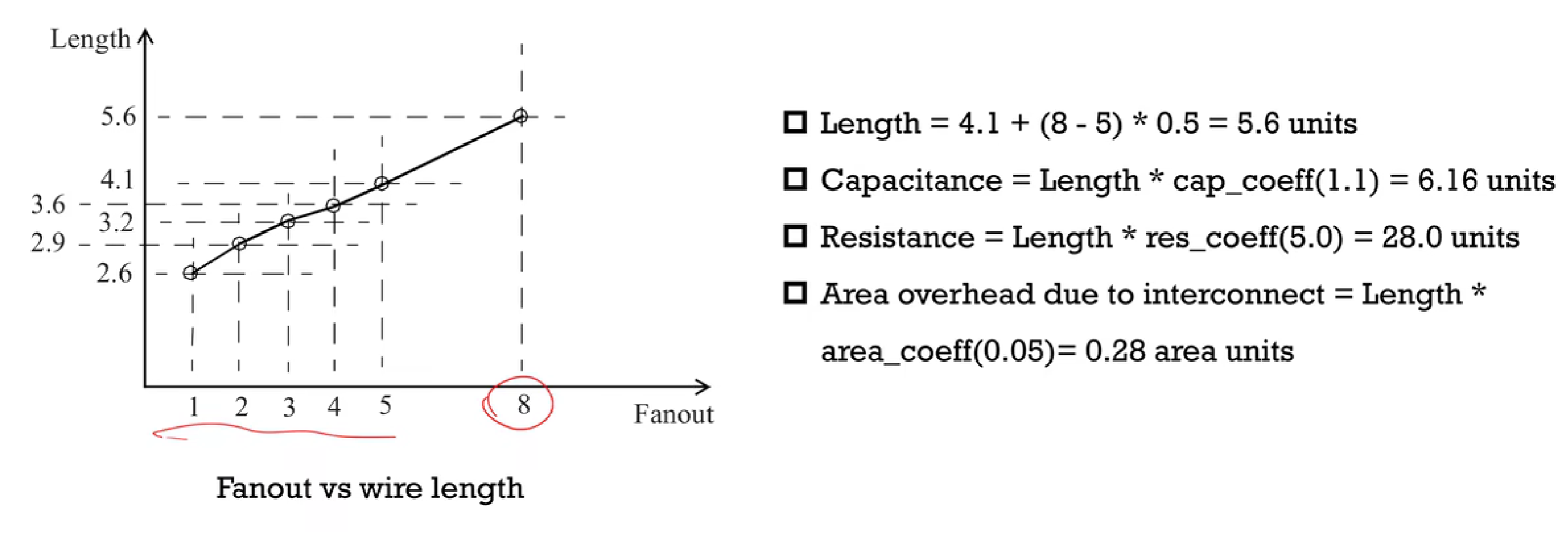

线载模型里面定义有模型名,电阻电容,面积,扇出与长度的对应关系。

其中斜率slope用于对应扇出没有在模型中定义的情况下其他参数的计算,如下图所示。

STA环境

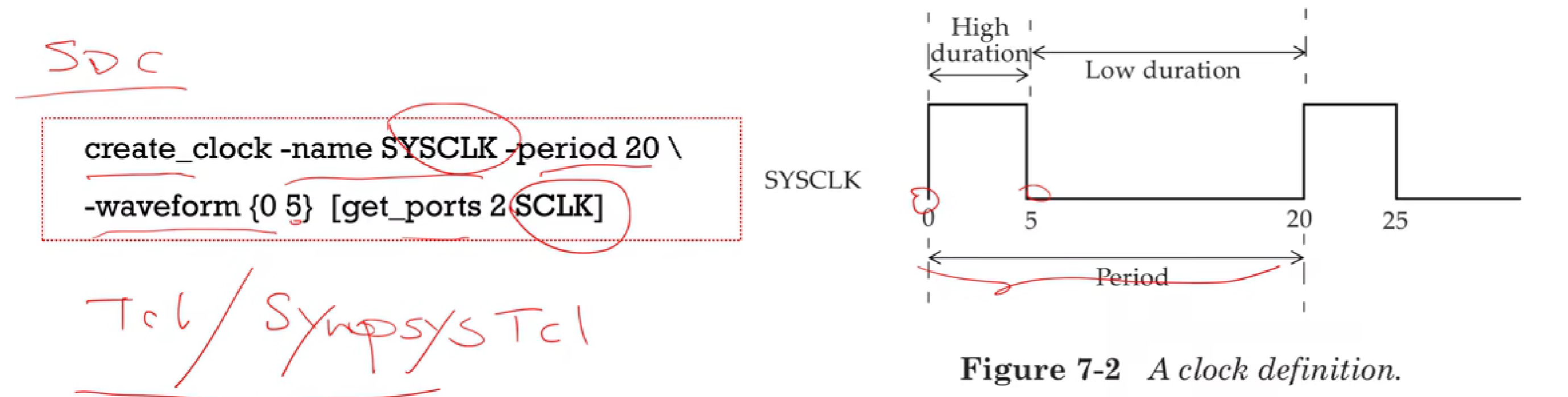

时钟定义

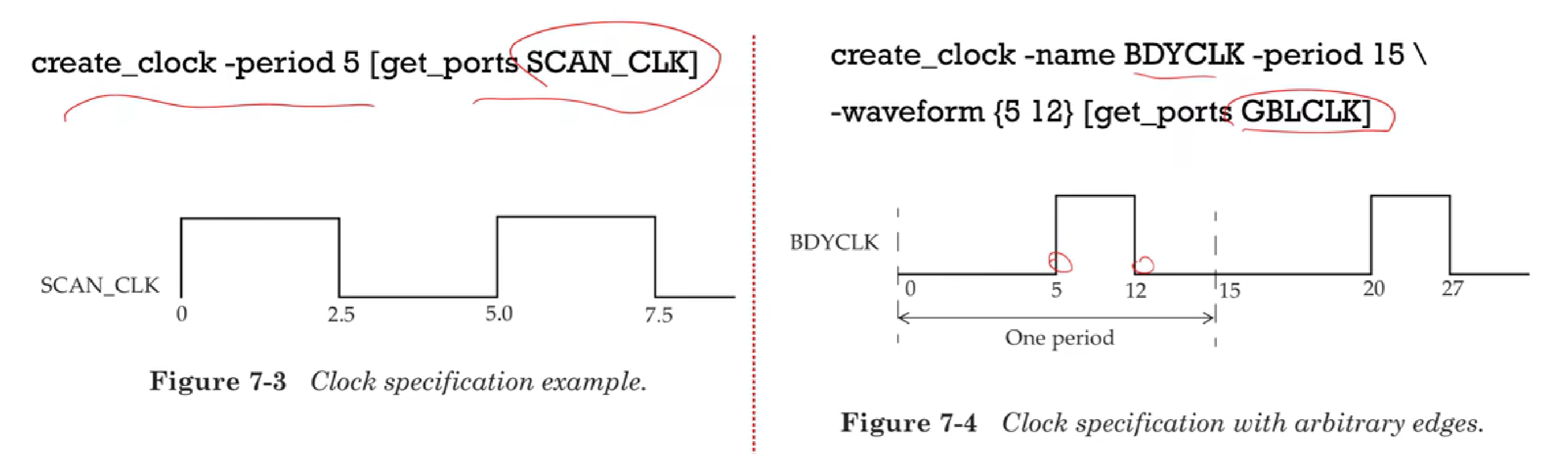

定义一个时钟:

- 时钟源:一个端口、pin或者一个cell

- 时钟周期

- 占空比:高电平比上周期

- 边缘翻转时间

下面是使用tcl定义时钟的一个例子,时钟周期为20ns,在0和5时间进行翻转(定义波形)

还有其他定义方法

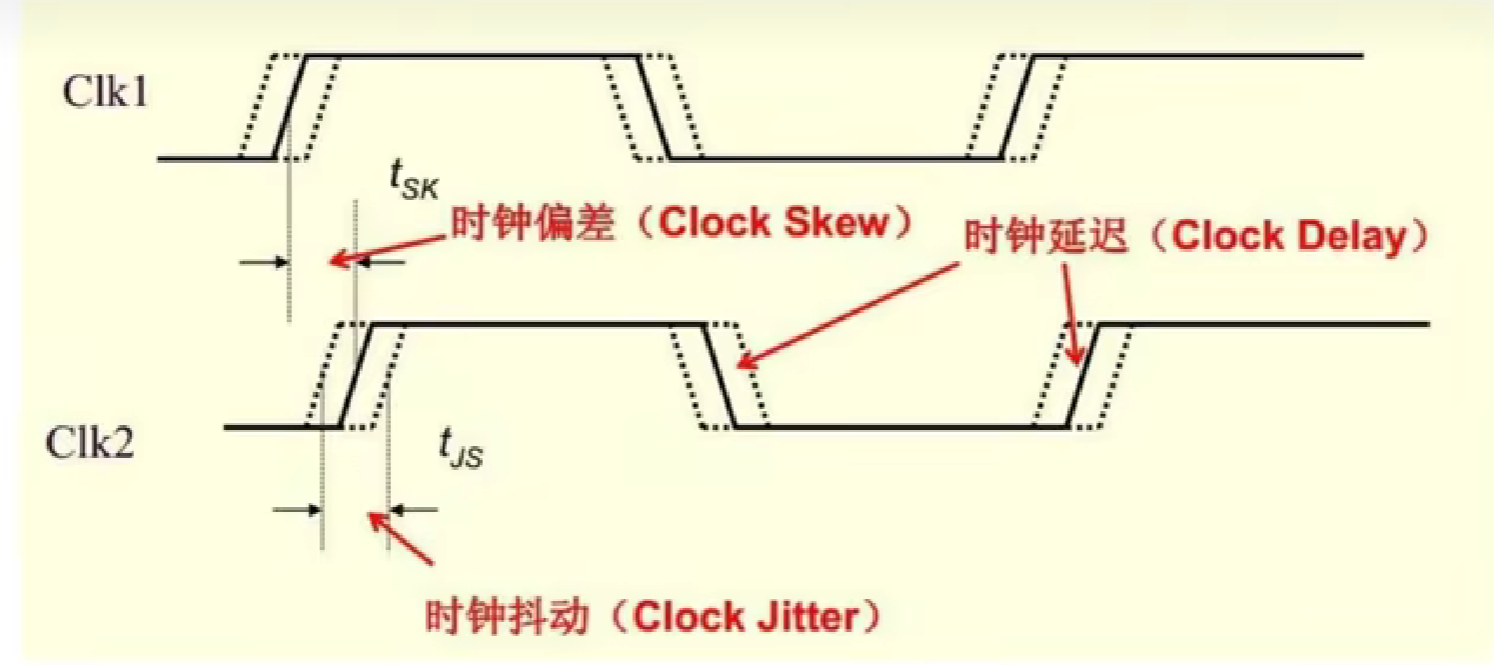

时钟偏差(skew),时钟抖动(jitter),时钟延迟(delay),建立时间,保持时间均可使用tcl来进行定义。定义时钟不确定性约束可以让电路更加稳健。

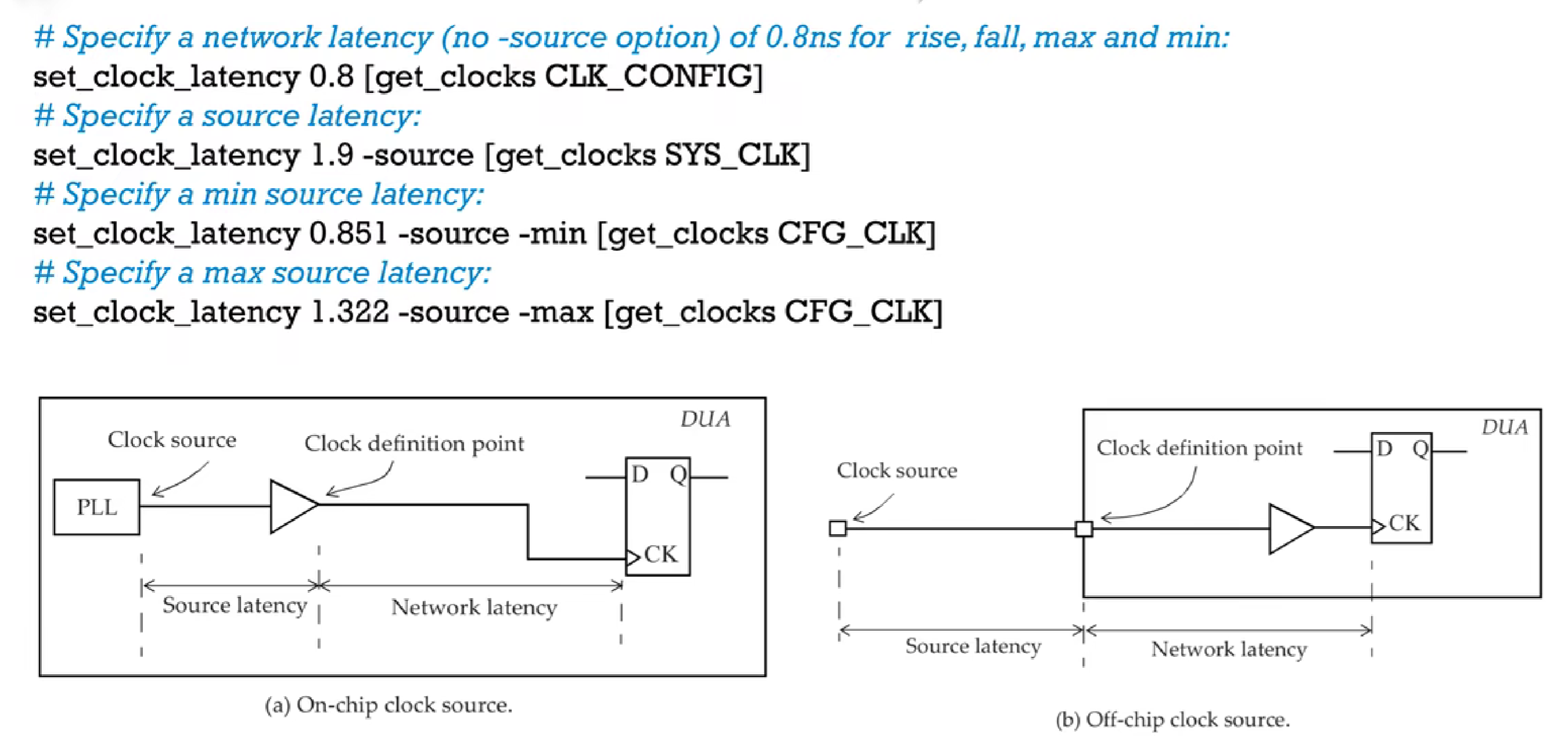

时钟延迟包括时钟源延迟和时钟网络延迟,在定义时钟延迟的时候需要进行区分。

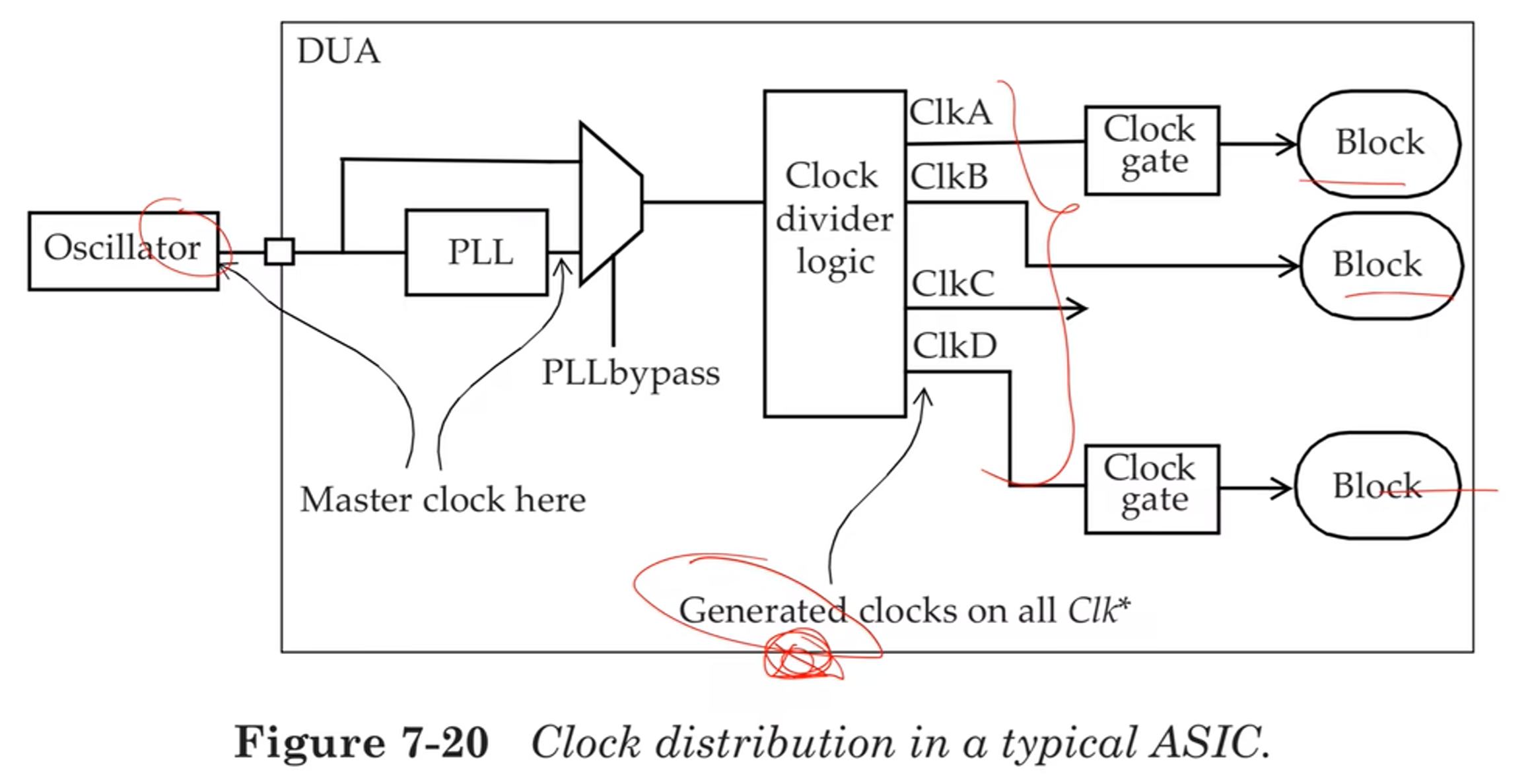

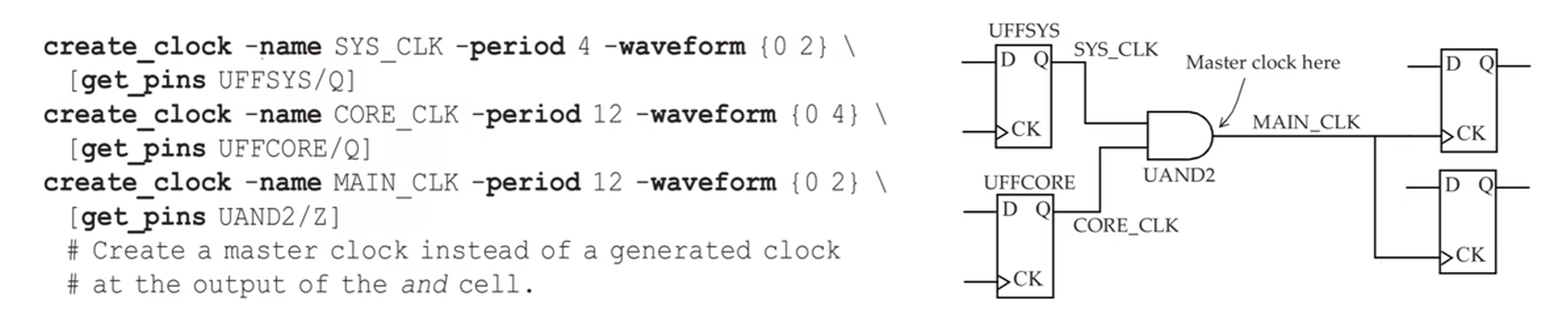

master时钟与生成时钟

创建生成时钟的例子,注意与创建时钟的区别,需要使用-source指定一个master时钟。一般用于创建分频时钟。

不能把一个生成时钟定义成一个master时钟:

- 否则综合工具会认为这个时钟也是一个master时钟,两个时钟之间没有关联,导致这条时序路径被认为是异步时钟,无法进行sta。

- generated_clock的时钟延迟能够累加,master之间的时钟延迟无法累加。

- 不一定都要定义成generated_clock,下面的例子可以将MAIN_CLK定义成一个新的master

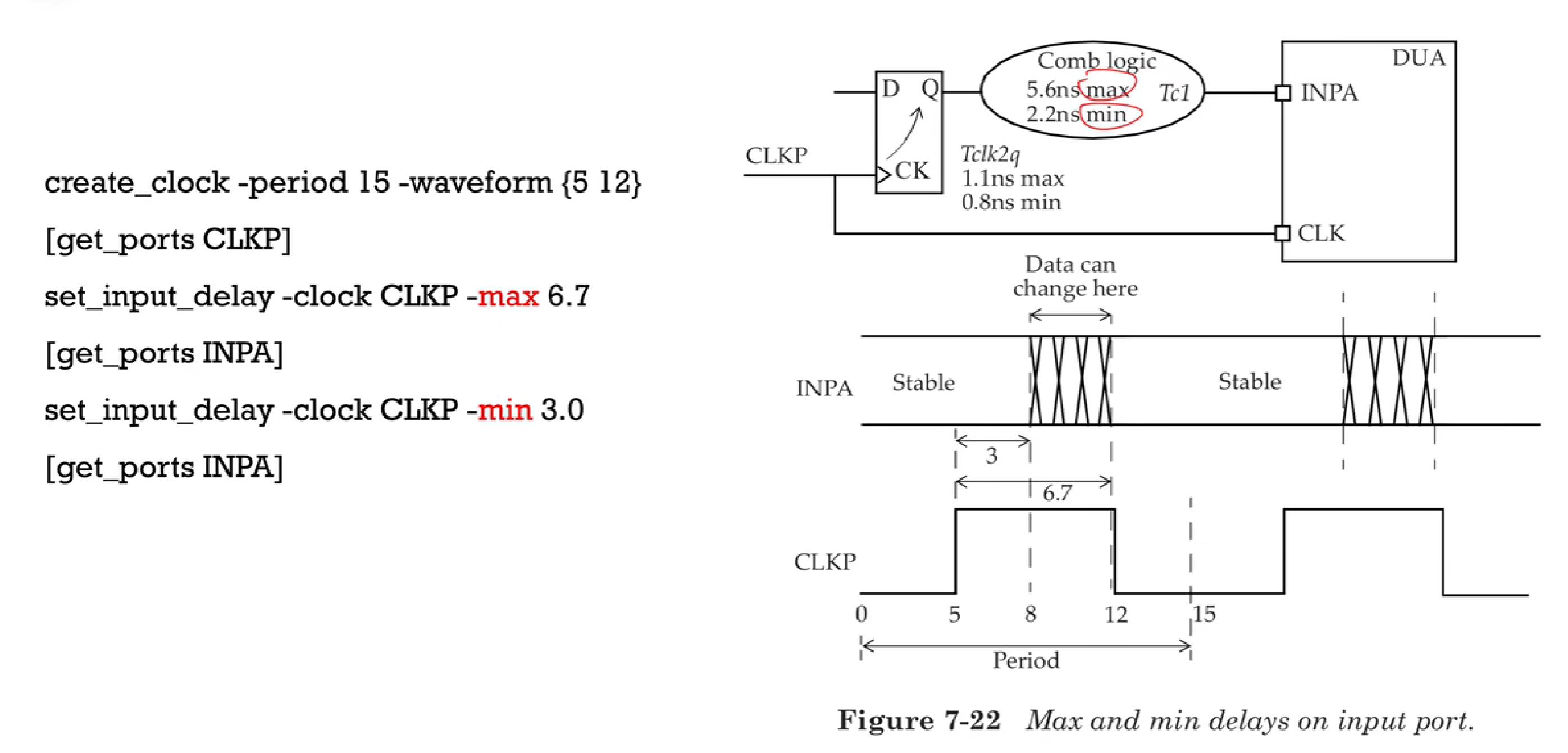

输入输出引脚的约束

有4种时序路径需要分析,对于非reg-reg类型的路径,需要指定输入约束(输入最大延迟与最小延迟)与输出约束才能进行计算。输出约束是为了让外部逻辑进行时序分析。

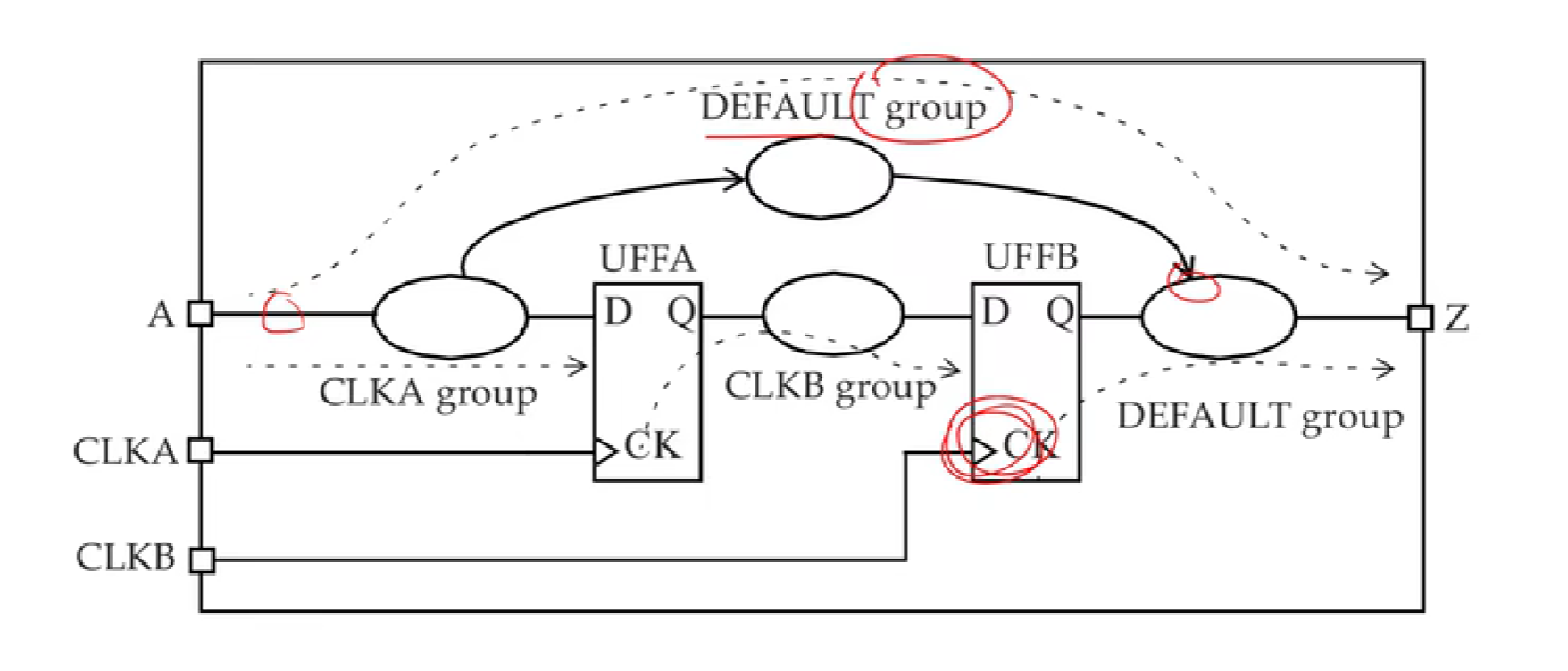

时序路径组:根据路径终点进行分类,同一终点的路径属于同一个时序路径组。

IO属性

当设置了creat_clock、set_input_delay 和 set_output_delay这些约束就足够对一个设计内部的时序路径进行时序分析,但是对IO引脚还需要额外的约束才能更精确。

- 对于输入:set_drive,set_driving_cell,set_input_transition(这三个属性设置一个即可),如果没有设置,默认为理想输入,即set_drive 0 [get_ports UCLK]

- 对于输出:set_load

DRC

通过设置最大转换时间和最大电容来进行design rule check。会检查所有的端口和引脚是否满足这些规则。通常设置的比库更小,以满足更严格的时序要求。

1 | set_max_transition 0.6 IOBANK # 设置IOBANK的最大转换时间为600ps |

还可以为设计指定其他设计规则检查。set_max_fanout(指定设计中所有引脚的fanout限制),set_max_area(用于设计);然而,这些检查只适用于 synthesis ,而不适用于STA。

虚拟时钟

虚拟时钟通常应用于设定输入和输出的延迟,即set_input_delay和set_output_delay。在设定延迟的时候要指定一个时钟,一般指定为虚拟时钟。

主时钟要指定时钟输入端口,虚拟时钟不用指定

1 | create_clock -name sysclk -period 10 [get_ports clkin] |

加快分析

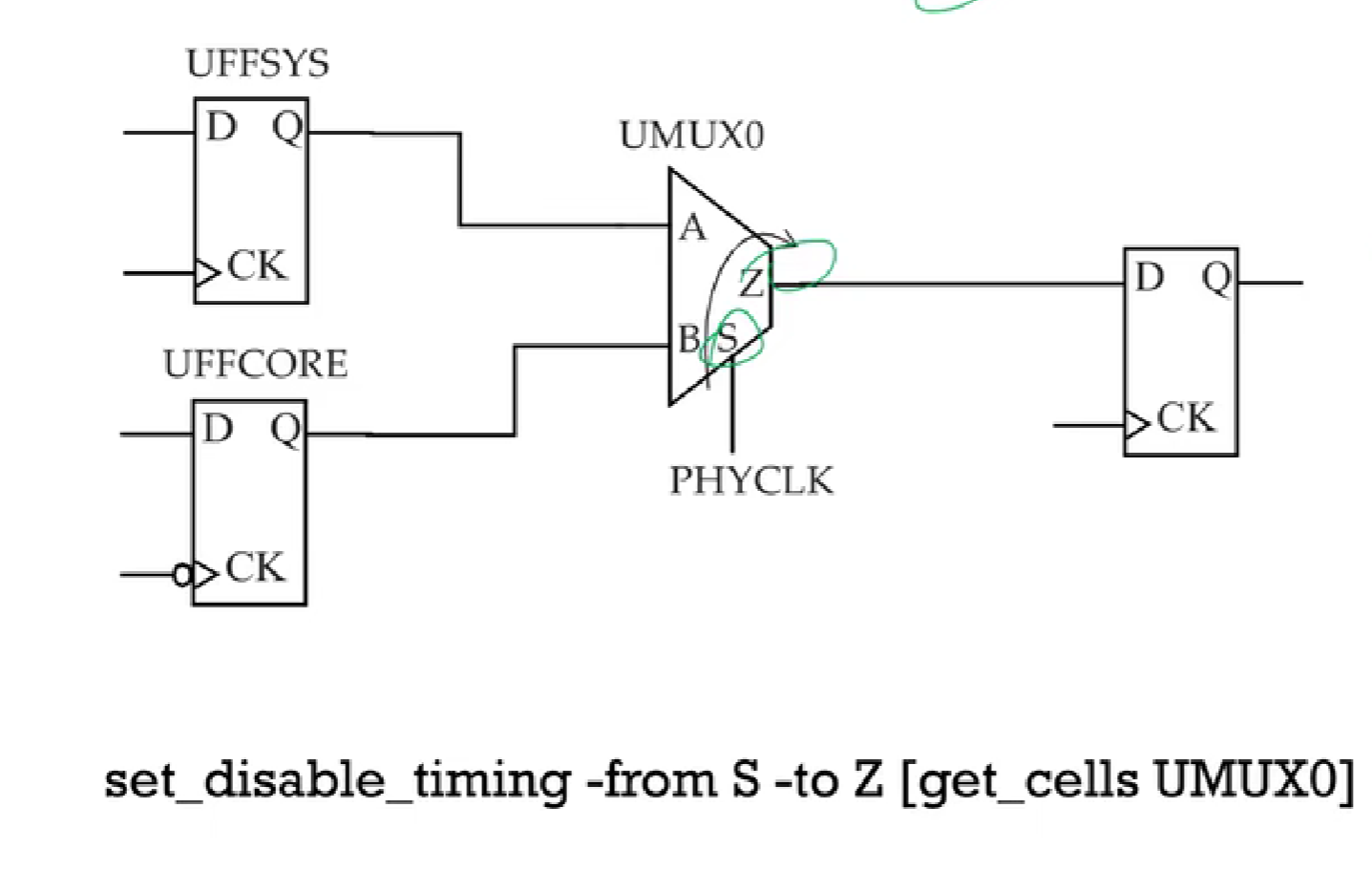

使用set_disable_timing来关闭某个路径的分析,下图关闭了UMUX0中从S到Z的时序分析。

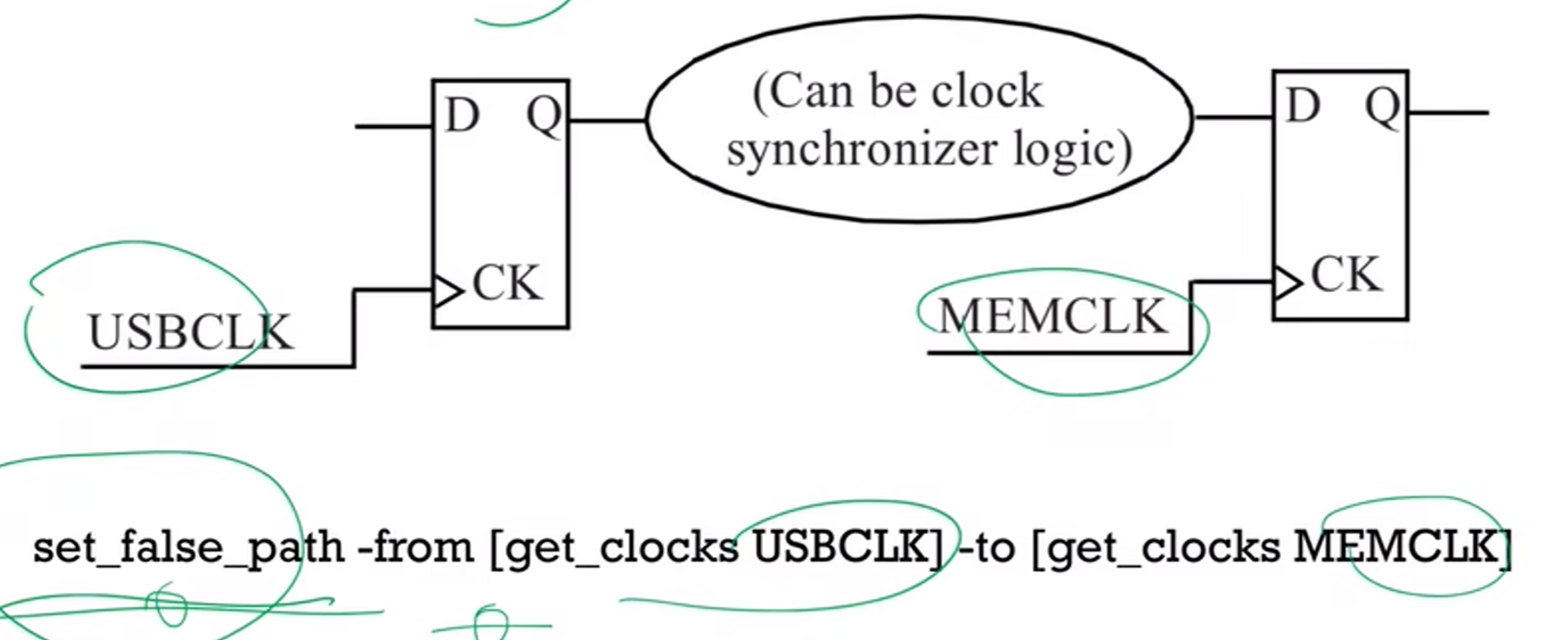

对于跨时钟域电路,异步电路,需要使用set_false_path来说明是伪路径,不进行时序分析

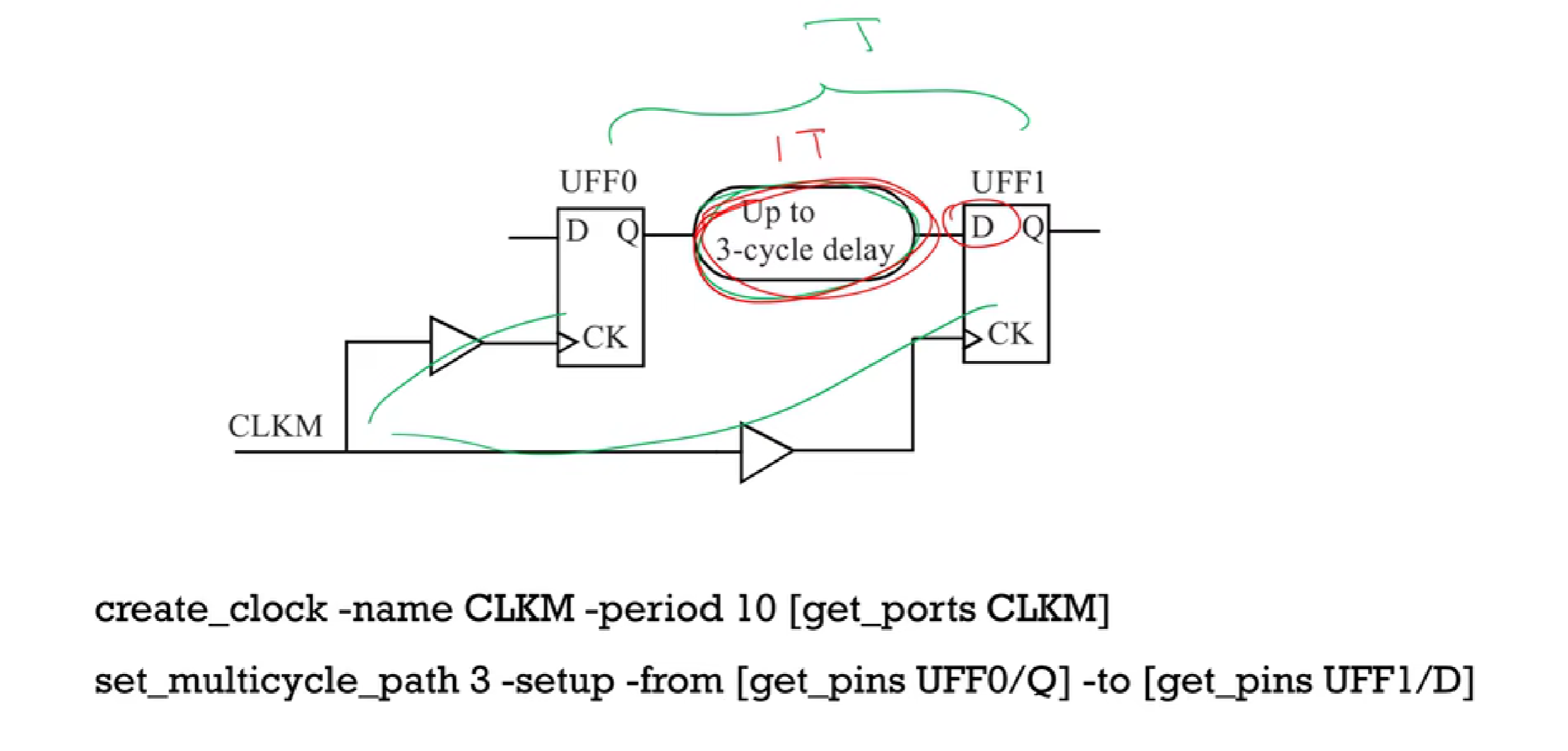

默认的sta检查为单周期,对于多周期路径,只对最后一个周期进行检查。需要使用set_multicycle_path来指明多周期路径和周期数。前端需要把多周期与伪路径告诉后端(后端并不知道)

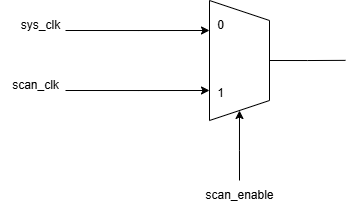

一个设计在某些模式下,有部分信号可能是个常数值,比如用于dft的测试电路的时钟scan_clk。此时可以用set_case_analysis来固定多路选择器的值,不分析测试电路的时序。

1 | set_case_analysis 0 [get_ports scan_enable] |

建立时间与保持时间

两种时序的理解参考博客https://www.cnblogs.com/lilto/p/9581143.html

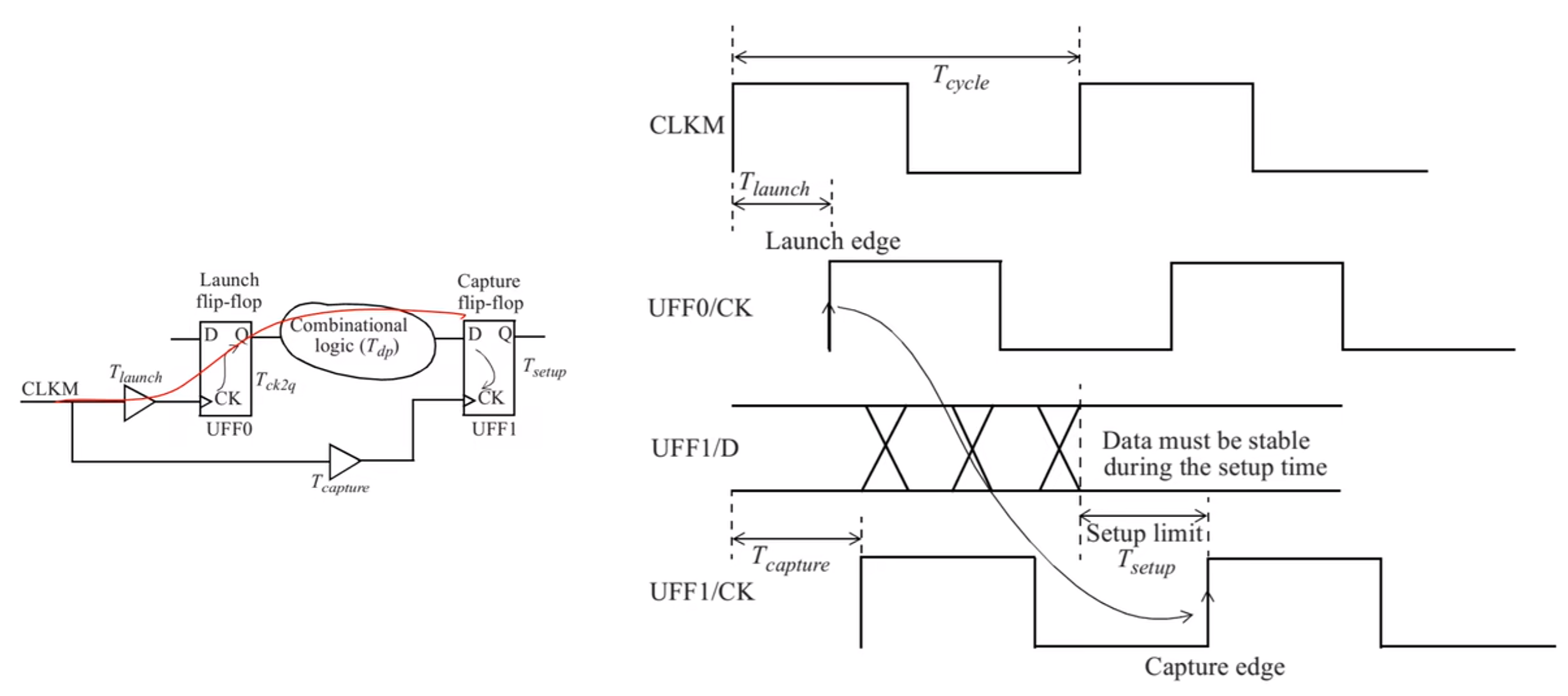

分析方法,画图分析更清晰!保持时间的检查是在建立时间的前一时钟沿

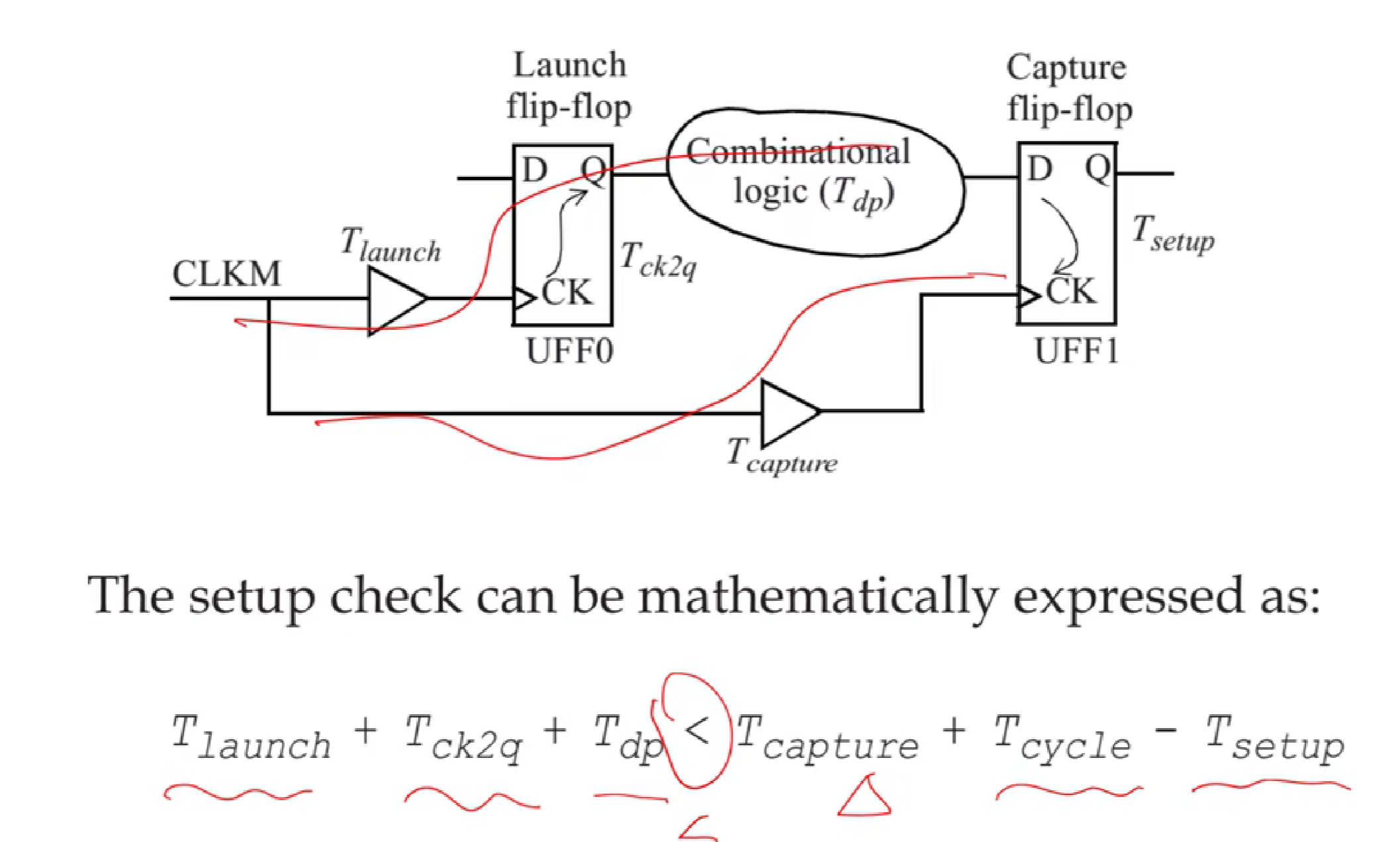

建立时间

建立时间是在下一时钟沿进行检查。

建立时间要用延迟最大的情况进行检查,如果延迟最大的情况仍满足建立时间的要求,则其他情况也能满足要求。

建立时间的要求如下,要求数据需要时间(右侧)大于数据到达时间(左侧),两者的差(slack)要大于等于0。在实际情况下数据到达时间还要减去设定的clock uncertainty的值。

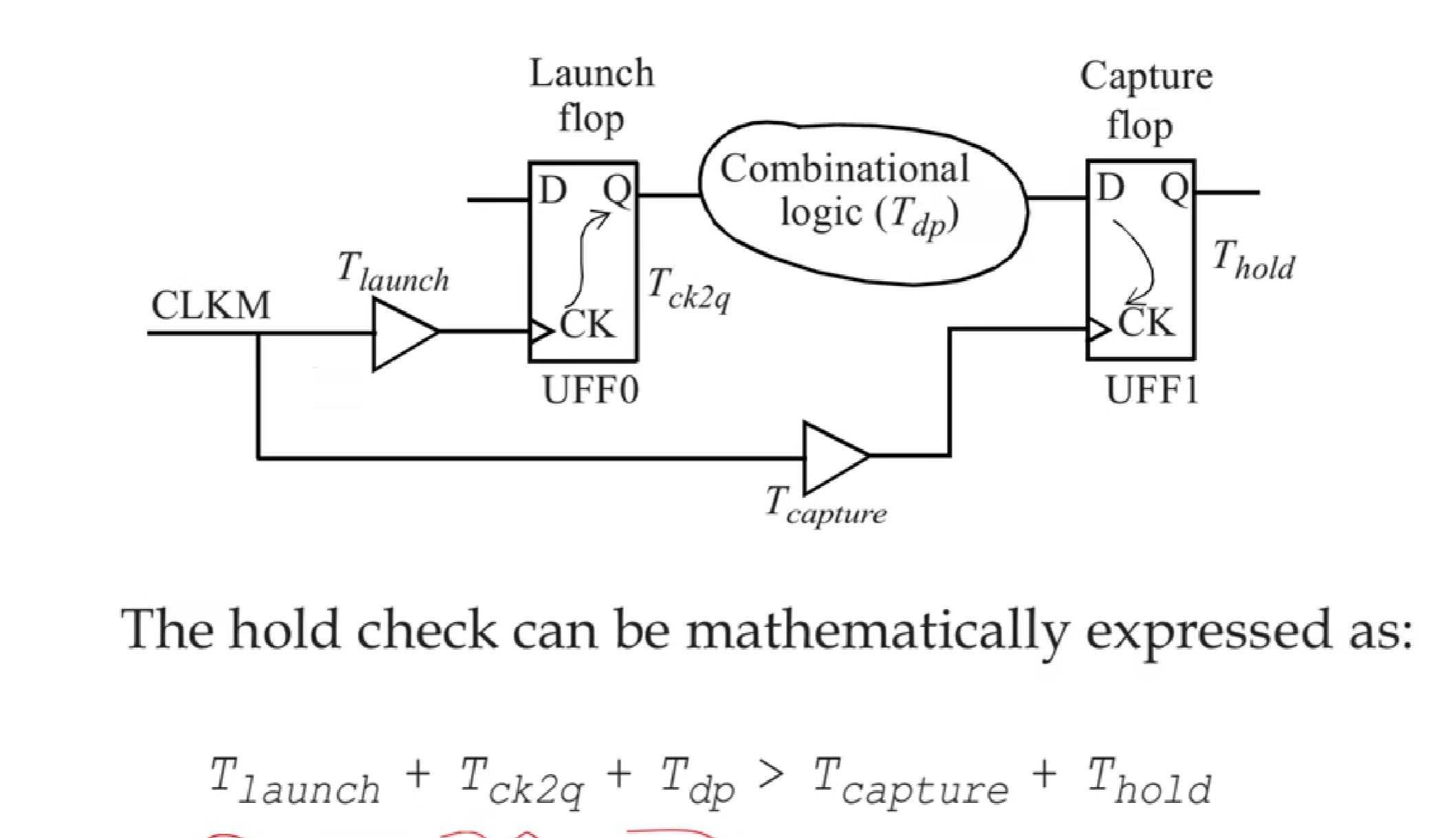

保持时间

保持时间是在同一时钟沿进行检查,新的数据到达的时间要在保持时间之后。保持时间要在延迟最小的时间进行检查。

保持时间时间的要求如下,要求数据需要时间(右侧)小于数据到达时间(左侧),两者的差(slack)要大于等于0。在实际情况下数据需要时间还要加上设定的clock uncertainty的值。

主要要看懂时序报告

多周期路径的检查

如果设定了一条路径是多周期路径,如果设置建立时间的检查为第N个周期,在检查建立时间的时候,数据需要时间是加上N个T,而不是一个T。

一般设定保持时间的检查时间在第N-1个周期,则保持时间的数据需要时间要加上N-1个T。单周期路径上,建立时间检查为第1个周期,保持时间为第0个周期,因此建立时间检查要加上一个T,而保持时间没有。

要合理设置检查的时间点,否则会导致保持时间无法满足!

半周期路径的检查

这种情况发生在一个寄存器在下降沿触发,另一个在上升沿触发。半周期路径只有T/2个周期的余量,建立时间要求更高。

半周期路径的特点是建立时间要求很高,但是保持时间容易满足要求。而建立时间更好修一点,因此可以得到一个启发:

- 跨芯片的路径可以设置为半周期路径,能容易满足保持时间的要求